## USN

# Third Semester B.E. Degree Examination, Dec.2018/Jan.2019 **Analog and Digital Electronics**

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

### Module-1

- Explain construction and working principle of operations of n-channel D-MOSFET along 1 with its drain and trans-conductance characteristics. (10 Marks)

- Write the difference between JEFT's and MOSFET's.

(05 Marks)

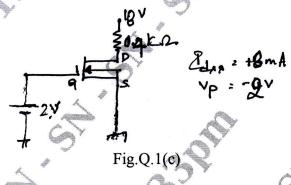

For a given self-bias configuration in Fig.Q.1(c), determine: i)  $I_{da}$  and  $V_{g'eq}$  ii)  $V_{ds}$  and  $V_{D}$ .

(05 Marks)

List of differences between ideal and practical op-amp amplifier.

(06 Marks)

- With a neat diagram and waveform explain astable multivibrator using 555 timers. (07 Marks) b.

- With neat diagram and waveform explain the working of relaxation oscillation oscillator.

(07 Marks)

### Module-2

Explain positive and negative logic. List the equivalence between them. 3

(08 Marks)

Find the minimal SOP form for the given min-terns using K-map.

$F(A, B, C, D) = \sum m(4, 5, 6) + d(10, 12, 13, 14, 15).$

(06 Marks)

c. Find the minimal POS form for the given MAX-TERM using K-map.

$f(a, b, c, d) = \pi M (5, 7, 8, 9, 12) + d(0, 6, 10, 15).$

(06 Marks)

Using Quine-Mc-Clusky method simplify the following Boolean equation.

$f(a, b, c, d) = \sum_{m} (0, 1, 10, 11, 13, 15) + d(2, 3, 12, 14).$

(10 Marks)

b. Define Hazard. Explain different types of Hazards.

(06 Marks)

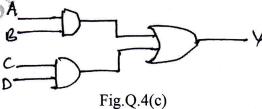

Write the VHDL code for the circuit shown in Fig.Q.4(c):

(04 Marks)

1 of 2

2. Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8=50, will be treated as malpractice. Important Note: 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

|    |     | Module-3                                                                                                                                                  | (08 Marks)    |

|----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 5  | a.  | What is multiplexers? Design 8:1 multiplexer using 2:1 multiplexers.                                                                                      |               |

|    | b.  | What is multiplexers? Design 8:1 multiplexer using 2.7 materials. Explain the purpose of using parity generators and checkers using suitable illustrates. | (06 Marks)    |

|    | U.  |                                                                                                                                                           | (06 Marks)    |

|    | c.  | What is magnitude comparator? Explain 1 bit magnitude comparator.                                                                                         | (00 Marks)    |

|    |     | A Y                                                                                                                                                       |               |

|    |     | OR                                                                                                                                                        | (06 Marks)    |

| 6  | a.  | Design 7-segment decoder using PLA.                                                                                                                       |               |

| U  | b.  | Design 7-segment decoder using FLA.  With neat logic diagram and truth table, explain negative edge triggered J-K flip-f                                  | (06 Marks)    |

|    | 0.  | A 11 1 16 Adder full Adder half suh                                                                                                                       | stractor and  |

|    | c.  | What is an Adder? Explain with truth table the half Adder, full Adder, half sub                                                                           | (08 Marks)    |

|    |     | full subtractor.                                                                                                                                          | (00 11241115) |

|    |     |                                                                                                                                                           |               |

|    |     | Module-4                                                                                                                                                  | ve flip-flop  |

| 7  | a.  |                                                                                                                                                           | (08 Marks)    |

|    |     | using NAND gates.                                                                                                                                         |               |

|    | b.  | Give characteristic table, characteristic equation and excitation table for S-R,                                                                          | (08 Marks)    |

|    |     | flip-flop.                                                                                                                                                | (04 Marks)    |

|    | c.  | Write a VHDL code for D-flip-flop.                                                                                                                        | (0.1.2)       |

|    |     |                                                                                                                                                           |               |

|    |     | UK    A lain 4 hit parallel in serial out shift reg                                                                                                       | ister.        |

| 8  | a.  | What is a register? With neat diagram explain 4-bit parallel-in-serial out shift reg                                                                      | (08 Marks)    |

|    |     | Explain with a neat diagram how a shift register can be applied for serial-addition                                                                       | n.            |

|    | b.  | Explain with a neat diagram now a sinit register can be applied to                                                                                        | ,             |

|    |     | . Differentiate between synchronous and asynchronous counters.                                                                                            | (06 Marks)    |

|    | C.  | . Differentiate between synone as and                                                                                                                     |               |

|    | *   | Module-5                                                                                                                                                  |               |

| 0  |     | D. C. Design & synchronous counter for the sequence.                                                                                                      |               |

| 9  | a   | $0 \rightarrow 3 \rightarrow 1 \rightarrow 2 \rightarrow 6 \rightarrow 7 \rightarrow 0 \rightarrow 3 \text{ using J-K flip flop.}$                        | (12 Marks)    |

|    | h   |                                                                                                                                                           | (08 Marks)    |

|    | U   | Explain with neat diagram the working principle of Digital Clock.                                                                                         |               |

|    |     | OR                                                                                                                                                        |               |

| 10 | Λ . | - 1 11 - 11 - 11 - 11 - 11 - 11 - 11 -                                                                                                                    | (06 Marks)    |

| 10 |     | Explain 2-bit simultaneous A/D converter.                                                                                                                 | (08 Marks)    |

| E  |     | To the terminal accuracy and resolution for D/A CONVELLEIS.                                                                                               | (06 Marks)    |

|    | (   | Explain the terms accuracy and resolution for Evilonical                                                                                                  |               |

|    |     |                                                                                                                                                           |               |

|    | 1   | ****                                                                                                                                                      |               |

|    | *   |                                                                                                                                                           |               |

|    |     |                                                                                                                                                           |               |

|    |     |                                                                                                                                                           |               |

|    |     |                                                                                                                                                           | (4)           |

|    |     |                                                                                                                                                           |               |

|    |     |                                                                                                                                                           | - Na          |

|    |     |                                                                                                                                                           |               |

|    |     |                                                                                                                                                           |               |

|    |     |                                                                                                                                                           |               |

|    |     |                                                                                                                                                           |               |

|    |     |                                                                                                                                                           |               |

|    |     | 2 of 2                                                                                                                                                    |               |

|    |     |                                                                                                                                                           |               |

|    |     |                                                                                                                                                           |               |

|    |     |                                                                                                                                                           |               |

|    |     |                                                                                                                                                           |               |

|    |     |                                                                                                                                                           |               |

|    |     | # Western C.                                                                                                                                              |               |